Right, latest update. the correct JTAG cable arrived today, so I fired up TopJTAG probe and started wiggling pins while monitoring, both on my scope and through the JTAG chain itself).

Looks like I was in the right ballpark with D31 on the local bus (data CPLD pin 94), but it turns out this side is just fine. Wiggling D31 on the local bus (and all other local data bus pins from the data CPLD) is reflected both externally via scope (measured at the FPU socket), and internally via JTAG chain.

The problem is actually with D31 on the A1200 bus side of the CPLD. Pin 52 to be precise. I've not exhaustively tested all pins of this bus, but of the pins I have tested, wiggling is reflected externally (seen on scope) and internally (seen on JTAG chain) on all pins *EXCEPT* D31.

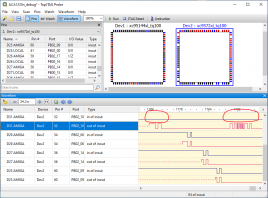

Driving D31 output high does not result in either the D31 CPLD input going high, nor is there any movement externally (measured at the expansion slot):

(Red circles show where I'd expect to see the activity on the output trace reflected, but clearly don't)

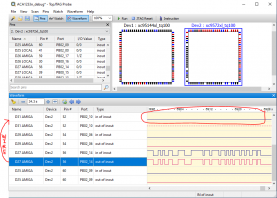

Just for fun, I also tried driving the (tristated) D31 pin with nearby D27, just to see if it was only the output driver, or also input receiver part of the I/O circuit that had died...

No movement on the D31 CPLD input, but wiggling was now observed on my scope at D31 on the expansion slot which tells me it's not a short to ground on the board... So, it looks like both input/output paths on Data CPLD pin 52 are dead! That certainly tallies with my earlier observation that transfers from the A1200 bus to the local bus were missing D31, it's just the failure was on the way into the CPLD, not out of it.

So yes, I guess the short version is 'Yep data CPLD definitely dead!'... cause of death?.... if I had to guess... maybe a rather catostophic ESD event on that pin when the previous owner shifted it between machines?

Sorry for the long winded waffling debug log. But hopefully the failure analysis may be of some use.

I'll now eagerly await availability of your mini CPLD boards in order to get hold of a replacement data CPLD... Unless you would be willing to give a secure remote-programming session a go? Let me know and I'll get my fresh XC9572XL soldered on!

As an aside... the packaging for the *single* XC9572XL CPLD I ordered is seriously impressive/overkill...

(A1200 for scale...  )

)

That's a whole 90 capacity IC tray vaccum packed with dessicant for a single CPLD! I guess that's the IC travel equivilent of turning up for a flight and being bumped up to first class on an empty plane!

All the best,

Graysters

![]()